An Intellectual Property (IP) core in Semiconductors is a reusable unit of logic or functionality or a cell or a layout design that is normally developed with the idea of licencing to multiple vendor for using as building blocks in different chip designs.

In today’s era of IC designs more and more system functionality are getting integrated into single chips (System on Chip /SOC designs). In these SOC designs, these pre-designed IP cores/blocks are becoming more and more important. This is because most of the SOC designs have a standard microprocessor and lot of system functionality which are standardized and hence if designed once can be re-used across several designs.

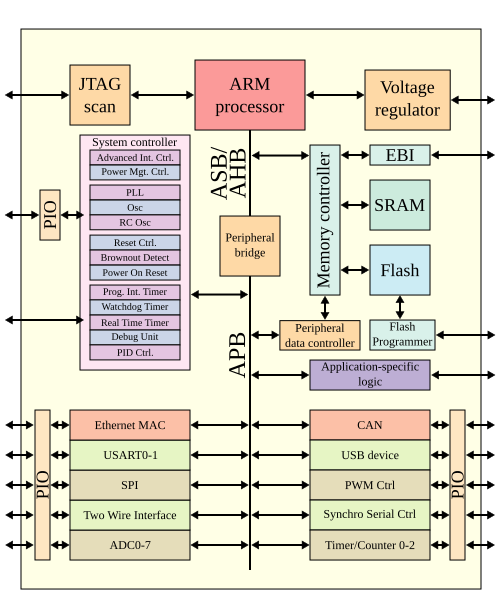

Refer following diagram (Reference wikipedia) and you can see that a lot of the components are standardized protocols and designs – eg the ARM bus protocols like AHB, APB, the designs like Ethernet, SPI, USB , UART core etc. All of these can be designed stand alone as IP cores/blocks and can be licenced to multiple design houses and for different designs.

IP cores are generally licensed as either Soft IP cores or Hard IP cores.

Soft IP cores are IP blocks generally offered as synthesizable RTL models. These are developed in one of the Hardware description language like SystemVerilog or VHDL.

Sometimes IP cores are also synthesized and provided as generic gate level netlist which can be then mapped to any process technologies. This also falls under Soft IP cores. The advantage of Soft IP cores is that those can be customized in the back end Placement and Routing flow by a consumer to map to any process technologies.

Hard IP cores on the other hand are offered as layout designs in a layout format like GDS which is mapped to a process technology and can be directly dropped by a consumer to the final layout of the chip. These cores cannot be customized for different process technologies.

Generally digital logic cores are developed and licensed as Soft IP cores. eg: a DRAM controller IP, Ethernet MAC IP, AMBA bus procotol IPs etc.

Analog and Mixed signal logic designs for serdes, PLLs, ADC or DAC, Phy layer logic for DDR, PCIE etc are generally developed and licensed as Hard IP cores.

With increased trend of IP based designs, there also came the need for Verification Intellectual Properties (VIPs).